# MOS INTEGRATED CIRCUIT

$\mu$ PD78011F(A), 78012F(A), 78013F(A), 78014F(A), 78015F(A), 78016F(A), 78018F(A)

## 8-BIT SINGLE-CHIP MICROCONTROLLER

#### DESCRIPTION

Compared to the  $\mu$ PD78018F (standard model), the  $\mu$ PD78018F(A) employs a stricter quality-assurance program. (NEC calls this quality grade "special grade").

The  $\mu$ PD78018F(A) is a product in the  $\mu$ PD78018F subseries within the 78K/0 series.

Compared with the older  $\mu$ PD78014 subseries, this subseries operates at lower voltage and provides a fuller set of ROM and RAM variations.

A one-time PROM model  $\mu$ PD78P018F(A) capable of operating in the same power supply voltage as of the mask ROM product and other development tools are also provided.

Functions are described in detail in the following User's Manual, which should be read when carring out design work.

$\mu$ PD78018F, 78018FY Subseries User's Manual : U10659E 78K/0 Series User's Manual – Instruction : U12326E

#### **FEATURES**

Large on-chip ROM & RAM

| Item         | Program         |                             | Data Memory              |            |                                     |

|--------------|-----------------|-----------------------------|--------------------------|------------|-------------------------------------|

| Product Name | Memory<br>(ROM) | Internal High-<br>Speed RAM | Internal<br>Expanded RAM | Buffer RAM | Package                             |

| μPD78011F(A) | 8K bytes        | 512 bytes                   | -                        | 32 bytes   | 64-pin plastic shrink DIP (750 mil) |

| μPD78012F(A) | 16K bytes       |                             |                          |            | • 64-pin plastic QFP (14 × 14 mm)   |

| μPD78013F(A) | 24K bytes       | 1024 bytes                  |                          |            |                                     |

| μPD78014F(A) | 32K bytes       |                             |                          |            |                                     |

| μPD78015F(A) | 40K bytes       |                             | 512 bytes                |            |                                     |

| μPD78016F(A) | 48K bytes       |                             |                          |            |                                     |

| μPD78018F(A) | 60K bytes       |                             | 1024 bytes               |            |                                     |

- External memory expansion space: 64K bytes

- I/O ports: 53 (N-ch open-drain: 4)

- 8-bit resolution A/D converter: 8 channels

- · Serial interface: 2 channels

- Timer: 5 channels

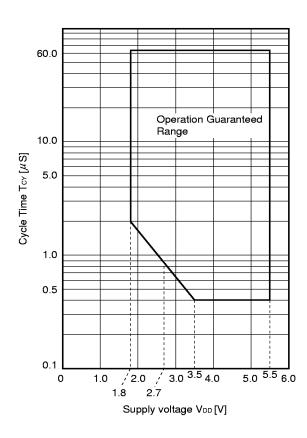

- Supply voltage: VDD = 1.8 to 5.5 V

In addition to the  $\mu$ PD78011F(A), 78012F(A), 78013F(A), 78014(A), 78015F(A), 78016F(A), and 78018F(A), this document also describes  $\mu$ PD78012F(A2). However, unless otherwise specified, the  $\mu$ PD78018F(A) is treated as the representative model throughout this document.

The information in this document is subject to change without notice.

Document No. U11921EJ2V0DS00 (2nd edition) Date Published August 1997 N Printed in Japan

The mark ★ shows major revised points.

### **APPLICATION**

Control unit of automotive, gas leak breaker, and safety devices, etc.

#### ORDERING INFORMATION

|   | Part Number                                  | Package                                |

|---|----------------------------------------------|----------------------------------------|

|   | μPD78011FCW (A)-×××                          | 64-pin plastic shrink DIP (750 mil)    |

|   | $\mu$ PD78011FGC (A)- $\times$ $\times$ -AB8 | 64-pin plastic QFP (14 × 14 mm)        |

|   | $\mu$ PD78012FCW (A)-×××                     | 64-pin plastic shrink DIP (750 mil)    |

|   | $\mu$ PD78012FGC (A)- $\times$ $\times$ -AB8 | 64-pin plastic QFP (14 $\times$ 14 mm) |

| 7 | $\mu$ PD78012FGC (A2)-×××-AB8                | 64-pin plastic QFP (14 × 14 mm)        |

|   | $\mu$ PD78013FCW (A)- $\times\times$         | 64-pin plastic shrink DIP (750 mil)    |

|   | $\mu$ PD78013FGC (A)-××-AB8                  | 64-pin plastic QFP (14 $\times$ 14 mm) |

|   | $\mu$ PD78014FCW (A)- $\times$ $\times$      | 64-pin plastic shrink DIP (750 mil)    |

|   | $\mu$ PD78014FGC (A)-××-AB8                  | 64-pin plastic QFP (14 $\times$ 14 mm) |

|   | $\mu$ PD78015FCW (A)- $\times\!\times$       | 64-pin plastic shrink DIP (750 mil)    |

|   | $\mu$ PD78015FGC (A)- $\times$ $\times$ -AB8 | 64-pin plastic QFP (14 $\times$ 14 mm) |

|   | $\mu$ PD78016FCW (A)- $\times$ $\times$      | 64-pin plastic shrink DIP (750 mil)    |

|   | $\mu$ PD78016FGC (A)- $\times$ $\times$ -AB8 | 64-pin plastic QFP (14 $\times$ 14 mm) |

|   | $\mu$ PD78018FCW (A)-×××                     | 64-pin plastic shrink DIP (750 mil)    |

|   | $\mu$ PD78018FGC (A)- $\times$ $\times$ -AB8 | 64-pin plastic QFP (14 $\times$ 14 mm) |

|   |                                              |                                        |

Remark xxx indicates a ROM code suffix.

### **QUALITY GRADE**

Special

Please refer to "Quality Grades on NEC Semiconductor Devices" (Document No. C11531E) published by NEC Corporation to know the specification of quality grade on the devices and its recommended applications.

## DIFFERENCES BETWEEN STANDARD MODEL AND (A) MODELS

| Product Names | (A) Models                                                              | Standard Model                                                                                               |

|---------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| Package       | 64-pin plastic shrink DIP (750 mil)     64-pin plastic QFP (14 × 14 mm) | 64-pin plastic shrink DIP (750 mil)     64-pin plastic QFP (14 × 14 mm)     64-pin plastic LQFP (12 × 12 mm) |

| Quality grade | Special                                                                 | Standard                                                                                                     |

## **\star** DIFFERENCES BETWEEN $\mu$ PD78012F(A) AND $\mu$ PD78012F(A2)

| Product Names                      | μPD78012F(A)                                                            | μPD78012F(A2)                     |  |

|------------------------------------|-------------------------------------------------------------------------|-----------------------------------|--|

| Item                               |                                                                         |                                   |  |

| Supply voltage                     | V <sub>DD</sub> = 1.8 to 5.5 V                                          | V <sub>DD</sub> = 5 V ± 10 %      |  |

| Operating temperature              | T <sub>A</sub> = -40 to +85 °C                                          | T <sub>A</sub> = -40 to +125 °C   |  |

| Minimum instruction execution time | 0.4 μs (at 10-MHz operation)                                            | 0.5 $\mu$ s (at 8-MHz operation)  |  |

| Package                            | 64-pin plastic shrink DIP (750 mil)     64-pin plastic QFP (14 × 14 mm) | • 64-pin plastic QFP (14 × 14 mm) |  |

**Remark** In addition to the above, the supply voltage and so on are different. For details, refer to **11. ELECTRICAL SPECIFICATIONS**.

2

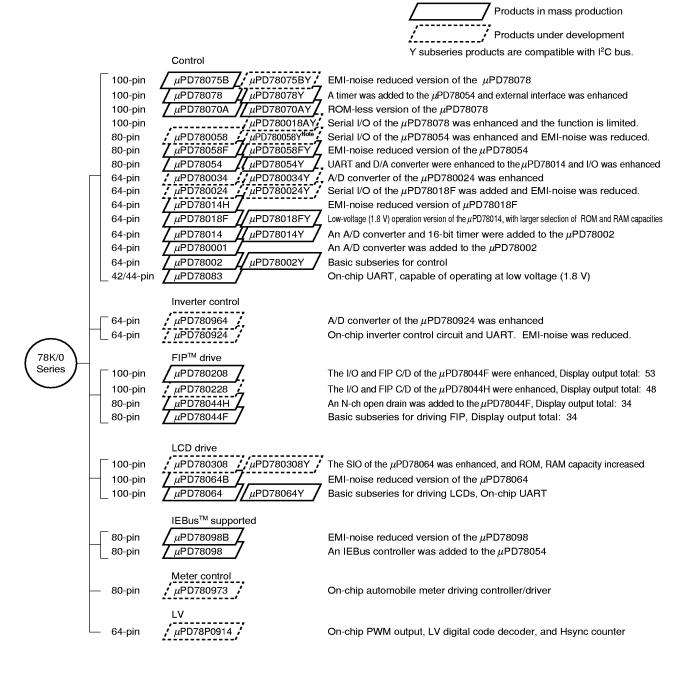

## ★ 78K/0 Series Expansion

The following shows the 78K/0 Series products development. Subseries name are shown inside frames.

Note Under planning

The following lists the main functional differences between subseries products.

|                  | Function   | ROM      |       | Tin    | ner   |     | 8-bit | 10-bit | 8-bit | Serial Interface              | 1/0 | V <sub>DD</sub> MIN. | External  |

|------------------|------------|----------|-------|--------|-------|-----|-------|--------|-------|-------------------------------|-----|----------------------|-----------|

| Subseries        | Name       | Capacity | 8-bit | 16-bit | Watch | WDT | A/D   | A/D    | D/A   | Serial interface              | 1/0 | Value                | Expansion |

| Control          | μPD78075B  | 32K-40K  | 4ch   | 1ch    | 1ch   | 1ch | 8ch   | -      | 2ch   | 3ch (UART: 1ch)               | 88  | 1.8 V                | 0         |

|                  | μPD78078   | 48K-60K  |       |        |       |     |       |        |       |                               |     |                      |           |

|                  | μPD78070A  | _        |       |        |       |     |       |        |       |                               | 61  | 2.7 V                |           |

|                  | μPD780058  | 24K-60K  | 2ch   |        |       |     |       |        | 2ch   | 3ch (time division UART: 1ch) | 68  | 1.8 V                |           |

|                  | μPD78058F  | 48K-60K  |       |        |       |     |       |        |       | 3ch (UART: 1ch)               | 69  | 2.7 V                |           |

|                  | μPD78054   | 16K-60K  |       |        |       |     |       |        |       |                               |     | 2.0 V                |           |

|                  | μPD780034  | 8K-32K   |       |        |       |     | _     | 8ch    | -     | 3ch (UART: 1ch,               | 51  | 1.8 V                |           |

|                  | μPD780024  |          |       |        |       |     | 8ch   | _      |       | time division 3-wire: 1ch)    |     |                      |           |

|                  | μPD78014H  |          |       |        |       |     |       |        |       | 2ch                           | 53  | 1.8 V                |           |

|                  | μPD78018F  | 8K-60K   |       |        |       |     |       |        |       |                               |     |                      |           |

|                  | μPD78014   | 8K-32K   |       |        |       |     |       |        |       |                               |     | 2.7 V                |           |

|                  | μPD780001  | 8K       |       | _      | -     |     |       |        |       | 1ch                           | 39  |                      | _         |

|                  | μPD78002   | 8K-16K   |       |        | 1ch   |     | _     |        |       |                               | 53  |                      | 0         |

|                  | μPD78083   |          |       |        | _     |     | 8ch   |        |       | 1ch (UART: 1ch)               | 33  | 1.8 V                | _         |

| Inverter         | μPD780964  | 8K-32K   | 3ch   | Note   | _     | 1ch | -     | 8ch    | -     | 2ch (UART: 2ch)               | 47  | 2.7 V                | 0         |

| control          | μPD780924  |          |       |        |       |     | 8ch   | -      |       |                               |     |                      |           |

| FIP              | μPD780208  | 32K-60K  | 2ch   | 1ch    | 1ch   | 1ch | 8ch   | -      | -     | 2ch                           | 74  | 2.7 V                | -         |

| drive            | μPD780228  | 48K-60K  | 3ch   | _      | _     |     |       |        |       | 1ch                           | 72  | 4.5 V                |           |

|                  | μPD78044H  | 32K-48K  | 2ch   | 1ch    | 1ch   |     |       |        |       |                               | 68  | 2.7 V                |           |

|                  | μPD78044F  | 16K-40K  |       |        |       |     |       |        |       | 2ch                           |     |                      |           |

| LCD              | μPD780308  | 48K-60K  | 2ch   | 1ch    | 1ch   | 1ch | 8ch   | -      | -     | 3ch (time division UART: 1ch) | 57  | 2.0 V                | -         |

| drive            | μPD78064B  | 32K      |       |        |       |     |       |        |       | 2ch (UART: 1ch)               |     |                      |           |

|                  | μPD78064   | 16K-32K  |       |        |       |     |       |        |       |                               |     |                      |           |

| IEBus            | μPD78098B  | 40K-60K  | 2ch   | 1ch    | 1ch   | 1ch | 8ch   | -      | 2ch   | 3ch (UART: 1ch)               | 69  | 2.7 V                | 0         |

| supported        | μPD78098   | 32K-60K  |       |        |       |     |       |        |       |                               |     |                      |           |

| Meter<br>control | μPD780973  | 24K-32K  | 3ch   | 1ch    | 1ch   | 1ch | 5ch   | _      | ı     | 2ch (UART: 1ch)               | 56  | 4.5 V                | _         |

| LV               | μPD78P0914 | 32K      | 6ch   | _      | _     | 1ch | 8ch   | _      | _     | 2ch                           | 54  | 4.5 V                | 0         |

Note 10-bit timer: 1 channel

## **OVERVIEW OF FUNCTION**

|                   | Product Name                    |                                                                                                                                                                |                                    |                                          |               |                  |              |              |  |

|-------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------------------------------------------|---------------|------------------|--------------|--------------|--|

| Item              |                                 | μPD78011F(A)                                                                                                                                                   | μPD78012F(A)                       | μPD78013F(A)                             | μPD78014F(A)  | μPD78015F(A)     | μPD78016F(A) | μPD78018F(A) |  |

| Internal          | ROM                             | 8K bytes                                                                                                                                                       | 16K bytes                          | 24K bytes                                | 32K bytes     | 40K bytes        | 48K bytes    | 60K bytes    |  |

| memory            | High-speed RAM                  | 512 bytes                                                                                                                                                      |                                    | 1024 bytes                               |               |                  | •            |              |  |

|                   | Expanded RAM                    |                                                                                                                                                                |                                    | _                                        |               | 512 bytes        |              | 1024 bytes   |  |

|                   | Buffer RAM                      | 32 bytes                                                                                                                                                       |                                    |                                          |               |                  |              |              |  |

| Memory s          | pace                            | 64K bytes                                                                                                                                                      |                                    |                                          |               |                  |              |              |  |

| General-p         | urpose registers                | 8 bits × 32 r                                                                                                                                                  | egisters (8 bit                    | s × 8 registers                          | imes 4 banks) |                  |              |              |  |

|                   | nstruction                      | On-chip min                                                                                                                                                    | imum instructi                     | on execution t                           | ime cycle mod | dification funct | tion         |              |  |

| execution<br>time | When main system clock selected | 0.4 μs/0.8 μ                                                                                                                                                   | s/1.6 μs/3.2 μ                     | s/6.4 μs (at 10                          | .0 MHz opera  | tion)            |              |              |  |

|                   | When subsystem clock selected   | 122 μs (at 3                                                                                                                                                   | 2.768 kHz ope                      | eration)                                 |               |                  |              |              |  |

| Instruction       | ı set                           | •                                                                                                                                                              | on/division (8<br>lation (set, re: | bits $\times$ 8 bits,10 set, test, boole | •             |                  |              |              |  |

| I/O ports         |                                 | Total                                                                                                                                                          |                                    | : 53                                     |               |                  |              |              |  |

|                   |                                 | CMOS input: 2 CMOS I/O: 47 N-channel open-drain I/O: (15 V withstand voltage): 4                                                                               |                                    |                                          |               |                  |              |              |  |

| A/D conve         | erter                           | <ul> <li>8-bit resolution × 8 channels</li> <li>Operable over a wide power supply voltage range: AVDD = 1.8 to 5.5 V</li> </ul>                                |                                    |                                          |               |                  |              |              |  |

| Serial inte       | rface                           | 3-wire serial I/O/SBI/2-wire serial I/O mode selectable: 1 channel     3-wire mode (on-chip max. 32 bytes automatic data transmit/receive function): 1 channel |                                    |                                          |               |                  |              |              |  |

| Timer             |                                 | 16-bit timer/event counter: 1 channel     8-bit timer/event counter: 2 channels     Watch timer: 1 channel     Watchdog timer: 1 channel                       |                                    |                                          |               |                  |              |              |  |

| Timer out         | out                             | 3 (14-bit PW                                                                                                                                                   | /M output × 1)                     | ı                                        |               |                  |              |              |  |

| Clock outp        | out                             | 39.1 kHz, 78.1 kHz, 156 kHz, 313 kHz, 625 kHz, 1.25 MHz (at main system clock 10.0 MHz operation), 32.768 kHz (at subsystem clock 32.768 kHz operation)        |                                    |                                          |               |                  |              |              |  |

| Buzzer ou         | tput                            | 2.4 kHz, 4.9 kHz, 9.8 kHz (at main system clock 10.0 MHz operation)                                                                                            |                                    |                                          |               |                  |              |              |  |

| Vectored          | Maskable                        | Internal: 8,                                                                                                                                                   | External: 4                        |                                          |               |                  |              |              |  |

| interrupt         | Non-maskable                    | Internal: 1                                                                                                                                                    | Internal: 1                        |                                          |               |                  |              |              |  |

| sources           | Software                        | 1                                                                                                                                                              |                                    |                                          |               |                  |              |              |  |

| Test input        |                                 | Internal: 1, External: 1                                                                                                                                       |                                    |                                          |               |                  |              |              |  |

| Supply voltage    |                                 | V <sub>DD</sub> = 1.8 to 5.5 V                                                                                                                                 |                                    |                                          |               |                  |              |              |  |

| Operating a       | mbient temperature              | T <sub>A</sub> = -40 to                                                                                                                                        | +85 °C                             |                                          |               |                  |              |              |  |

| Package           |                                 |                                                                                                                                                                | stic shrink DIP                    | ` '                                      |               |                  |              |              |  |

Caution Compared to the other models, the  $\mu$ PD78012F(A2) differs in terms of the voltage and supply current. Refer to DIFFERENCES BETWEEN  $\mu$ PD78012F(A) AND  $\mu$ PD78012F(A2).

## **CONTENTS**

| 1.  | PIN CONFIGURATION (Top View)                                                                                                                                                                                  | 7                                |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 2.  | BLOCK DIAGRAM                                                                                                                                                                                                 | 10                               |

| 3.  | PIN FUNCTIONS  3.1 PORT PINS  3.2 OTHER PORTS  3.3 PIN I/O CIRCUIT AND RECOMMENDED CONNECTION OF UNUSED PINS                                                                                                  | 11<br>12                         |

| 4.  | MEMORY SPACE                                                                                                                                                                                                  | 16                               |

| 5.  | PERIPHERAL HARDWARE FUNCTION FEATURES  5.1 PORTS  5.2 CLOCK GENERATOR  5.3 TIMER/EVENT COUNTER  5.4 CLOCK OUTPUT CONTROL CIRCUIT  5.5 BUZZER OUTPUT CONTROL CIRCUIT  5.6 A/D CONVERTOR  5.7 SERIAL INTERFACES | 18<br>19<br>20<br>22<br>22<br>23 |

| 6.  | INTERRUPT FUNCTIONS AND TEST FUNCTIONS                                                                                                                                                                        | 25                               |

| 7.  | EXTERNAL DEVICE EXPANTION FUNCTIONS                                                                                                                                                                           | 29                               |

| 8.  | STANDBY FUNCTIONS                                                                                                                                                                                             | 29                               |

| 9.  | RESET FUNCTIONS                                                                                                                                                                                               | 29                               |

| 10. | INSTRUCTION SET                                                                                                                                                                                               | 30                               |

| 11. | ELECTRICAL SPECIFICATIONS                                                                                                                                                                                     | 33                               |

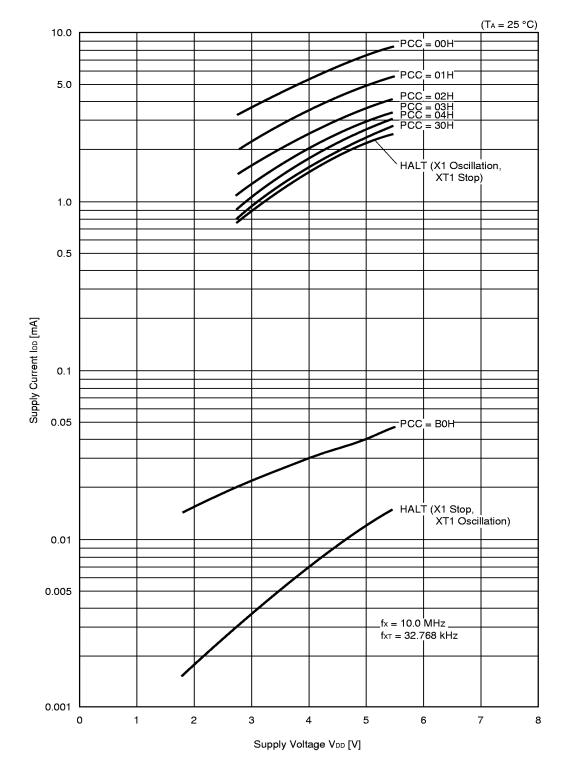

| 12. | CHARACTERISTIC CURVE (REFERENCE VALUES)                                                                                                                                                                       | 80                               |

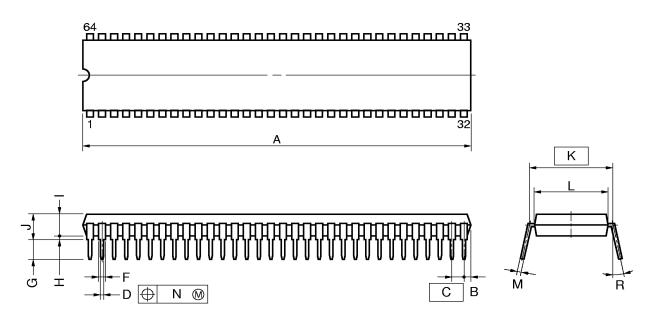

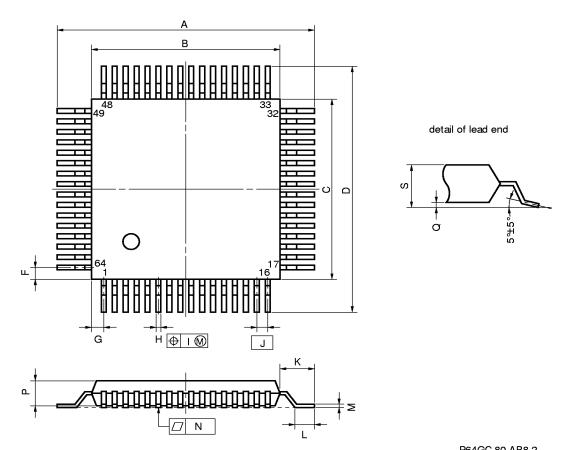

| 13. | PACKAGE DRAWINGS                                                                                                                                                                                              | 81                               |

| 14. | RECOMMENDED SOLDERING CONDITIONS                                                                                                                                                                              | 83                               |

| APF | PENDIX A. DEVELOPMENT TOOLS                                                                                                                                                                                   | 84                               |

| APF | PENDIX B. RELATED DOCUMENTS                                                                                                                                                                                   | 86                               |

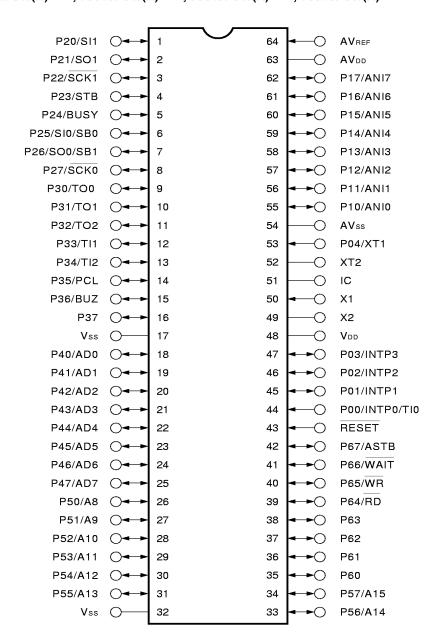

## 1. PIN CONFIGURATION (Top View)

• 64-Pin Plastic Shrink DIP (750 mil) μPD78011FCW(A)-xxx, 78012FCW(A)-xxx, 78013FCW(A)-xxx, μPD78014FCW(A)-xxx, 78015FCW(A)-xxx, 78016FCW(A)-xxx, 78018FCW(A)-xxx

Cautions 1. Always connect the IC (Internally Connected) pin to Vss directly.

- 2. Always connect the AVDD pin to VDD.

- 3. Always connect the AVss pin to Vss.

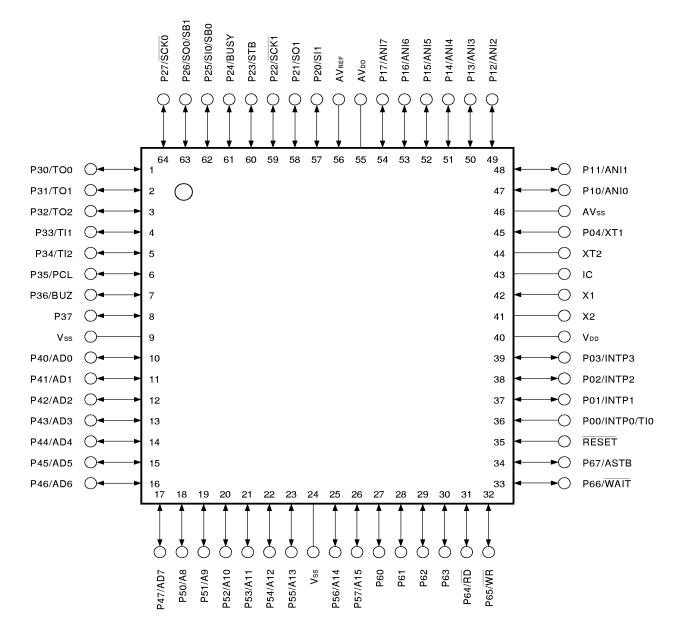

- 64-Pin Plastic QFP (14  $\times$  14 mm)

- ★  $\mu$ PD78011FGC(A)-××-AB8, 78012FGC(A)-××-AB8, 78012FGC(A2)-××-AB8, 78013FGC(A)-××-AB8,  $\mu$ PD78014FGC(A)-××-AB8, 78015FGC(A)-××-AB8, 78016FGC(A)-××-AB8, 78018FGC(A)-××-AB8

- Cautions 1. Always connect the IC (Internally Connected) pin to Vss directly.

- 2. Always connect the AVDD pin to VDD.

- 3. Always connect the AVss pin to Vss.

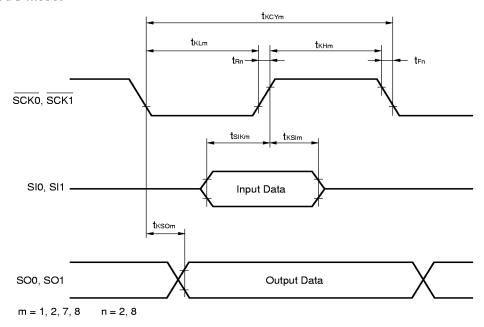

SO0, SO1

: Serial Output

A8 to A15 : Address Bus P60 to P67 : Port 6

AD0 to AD7 : Address/Data Bus **PCL** : Programmable Clock

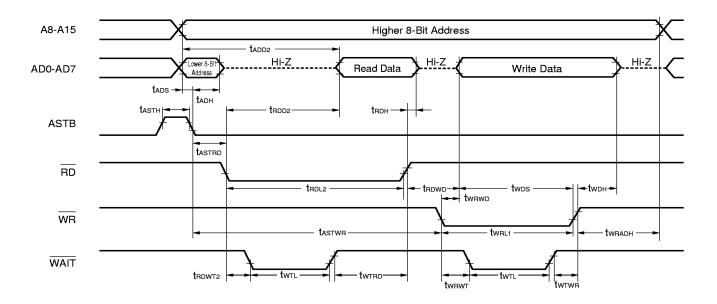

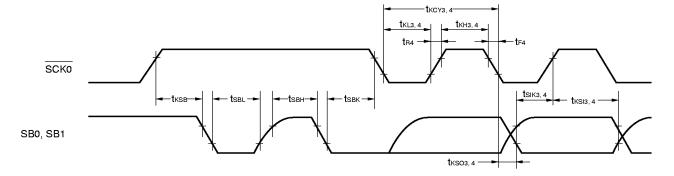

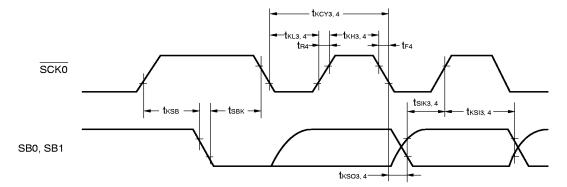

$\overline{RD}$ : Read Strobe ANI0 to ANI7 : Analog Input **ASTB** : Address Strobe RESET : Reset  $AV_{\text{DD}}$ : Analog Power Supply SB0, SB1 : Serial Bus SCKO, SCK1 : Serial Clock **AV**REF : Analog Reference Voltage : Analog Ground SIO, SI1 : Serial Input

$\mathsf{AV}_{\mathsf{SS}}$

**BUSY** : Busy

BUZ STB : Buzzer Clock : Strobe IC : Internally Connected TI0 to TI2 : Timer Input INTP0 to INTP3 : Interrupt from Peripherals TO0 to TO2 : Timer Output : Port 0  $V_{DD}$ : Power Supply

P00 to P04 P10 to P17 : Port 1 Vss : Ground P20 to P27 : Port 2 WAIT : Wait P30 to P37 : Port 3  $\overline{\mathsf{WR}}$ : Write Strobe

P40 to P47 : Port 4 X1, X2

: Crystal (Main System Clock) P50 to P57 : Port 5 XT1, XT2 : Crystal (Subsystem Clock)

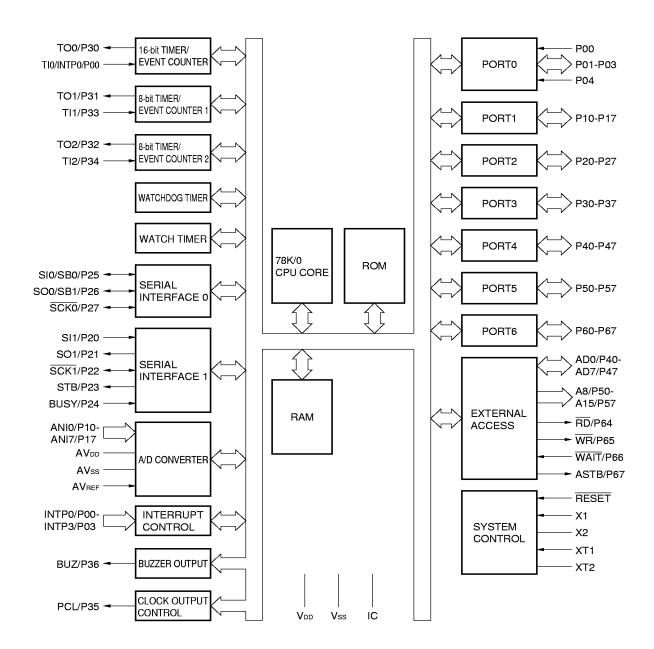

## 2. BLOCK DIAGRAM

Remark Internal ROM & RAM capacity varies depending on the product.

### 3. PIN FUNCTIONS

## 3.1 PORT PINS (1/2)

| Pin Name   | I/O              |                                                                                                                                                                                                                          | Function                                                                       | On Reset | Dual-<br>Function Pin |

|------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|----------|-----------------------|

| P00        | Input            | Port 0 Input only                                                                                                                                                                                                        |                                                                                | Input    | INTP0/TI0             |

| P01        | Input/           | 5-bit I/O port                                                                                                                                                                                                           | Input/output can be specified bit-wise.                                        | Input    | INTP1                 |

| P02        | output           |                                                                                                                                                                                                                          | When used as an input port, on-chip pull-up resistor can be used by software.  |          | INTP2                 |

| P03        | 1                |                                                                                                                                                                                                                          | resistor can be used by software.                                              |          | INTP3                 |

| P04Note 1  | Input            |                                                                                                                                                                                                                          | Input only                                                                     | Input    | XT1                   |

| P10 to P17 | Input/<br>output | l                                                                                                                                                                                                                        | be specified bit-wise.<br>an input port, on-chip pull-up resistor can be       | Input    | ANIO to ANI7          |

| P20        | Input/           | Port 2                                                                                                                                                                                                                   |                                                                                | Input    | SI1                   |

| P21        | output           | 8-bit input/outpu                                                                                                                                                                                                        | •                                                                              |          | SO1                   |

| P22        | 1                | 1 ' '                                                                                                                                                                                                                    | be specified bit-wise.<br>In input port, on-chip pull-up resistor can be       |          | SCK1                  |

| P23        | 1                | used by softwar                                                                                                                                                                                                          |                                                                                |          | STB                   |

| P24        | 1                |                                                                                                                                                                                                                          |                                                                                |          | BUSY                  |

| P25        | 1                |                                                                                                                                                                                                                          |                                                                                |          | SI0/SB0               |

| P26        | 1                |                                                                                                                                                                                                                          |                                                                                |          | SO0/SB1               |

| P27        | 1                |                                                                                                                                                                                                                          |                                                                                |          | SCK0                  |

| P30        | Input/           | Port 3                                                                                                                                                                                                                   |                                                                                | Input    | TO0                   |

| P31        | output           | 8-bit input/outpu                                                                                                                                                                                                        | •                                                                              |          | TO1                   |

| P32        |                  | l ' '                                                                                                                                                                                                                    | be specified in 1-bit units.<br>In input port, on-chip pull-up resistor can be |          | TO2                   |

| P33        |                  | used by softwar                                                                                                                                                                                                          | e.                                                                             |          | TI1                   |

| P34        |                  |                                                                                                                                                                                                                          |                                                                                |          | TI2                   |

| P35        |                  |                                                                                                                                                                                                                          |                                                                                |          | PCL                   |

| P36        |                  |                                                                                                                                                                                                                          |                                                                                |          | BUZ                   |

| P37        |                  |                                                                                                                                                                                                                          |                                                                                |          | _                     |

| P40 to P47 | Input/<br>output | Port 4 8-bit input/output port. Input/output can be specified in 8-bit unit. When used as an input port, on-chip pull-up resistor can be used by software. Test input flag (KRIF) is set to 1 by falling edge detection. |                                                                                | Input    | AD0 to AD7            |

- **Notes 1.** When using the P04/XT1 pins as an input port, set 1 to bit 6 (REC) of the processor clock control register (PCC). Do not use the on-chip feedback resistor of the subsystem clock oscillator.

- 2. When using the P10/ANI0 to P17/ANI7 pins as the A/D converter analog input, on-chip pull-up resistor is automatically unused.

# 3.1 PORT PINS (2/2)

| Pin Name   | I/O              |                                                                                                                             | On Reset                                                 | Dual-<br>Function Pin |      |

|------------|------------------|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-----------------------|------|

| P50 to P57 | Input/<br>output | Port 5 8-bit input/output port. LED can be driven direct Input/output can be spec When used as an input p used by software. | Input                                                    | A8 to A15             |      |

| P60        | Input/           | Port 6                                                                                                                      | N-ch open-drain input/output port.                       | Input                 | _    |

| P61        | output           | 8-bit input/output port.                                                                                                    | On-chip pull-up resistor can be                          |                       |      |

| P62        |                  | Input/output can be specified bit-wise.                                                                                     | specified by mask option.<br>LED can be driven directly. |                       |      |

| P63        |                  | ·                                                                                                                           | ,                                                        |                       |      |

| P64        |                  |                                                                                                                             | When used as an input port, on-chip                      |                       | RD   |

| P65        |                  |                                                                                                                             | pull-up resistor can be used by soft-                    |                       | WR   |

| P66        | ]                |                                                                                                                             | ware.                                                    |                       | WAIT |

| P67        |                  |                                                                                                                             |                                                          |                       | ASTB |

## 3.2 OTHER PORTS (1/2)

| Pin Name | I/O     | Function                                                     | On Reset | Dual-<br>Function Pin |

|----------|---------|--------------------------------------------------------------|----------|-----------------------|

| INTP0    | Input   | External interrupt request input by which the effective edge | Input    | P00/TI0               |

| INTP1    |         | (rising edge, falling edge, or both rising edge and falling  |          | P01                   |

| INTP2    |         | edge) can be specified.                                      |          | P02                   |

| INTP3    |         | Falling edge detection external interrupt request input.     |          | P03                   |

| SI0      | Input   | Serial interface serial data input.                          | Input    | P25/SB0               |

| SI1      |         |                                                              |          | P20                   |

| SO0      | Output  | Serial interface serial data output.                         | Input    | P26/SB1               |

| SO1      |         |                                                              |          | P21                   |

| SB0      | Input   | Serial interface serial data input/output.                   | Input    | P25/SI0               |

| SB1      | /output |                                                              |          | P26/SO0               |

| SCK0     | Input   | Serial interface serial clock input/output.                  | Input    | P27                   |

| SCK1     | /output |                                                              |          | P22                   |

| STB      | Output  | Serial interface automatic transmit/receive strobe output.   | Input    | P23                   |

| BUSY     | Input   | Serial interface automatic transmit/receive busy input.      | Input    | P24                   |

## 3.2 OTHER PORTS (2/2)

| Pin Name        | I/O              | Function                                                                                                   | On Reset | Dual-<br>Function Pin |

|-----------------|------------------|------------------------------------------------------------------------------------------------------------|----------|-----------------------|

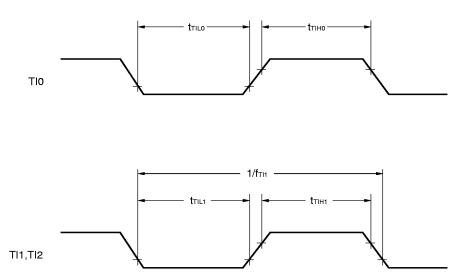

| TI0             | Input            | External count clock input to 16-bit timer (TM0).                                                          | Input    | P00/INTP0             |

| TI1             | 1                | External count clock input to 8-bit timer (TM1).                                                           | 1        | P33                   |

| TI2             | ]                | External count clock input to 8-bit timer (TM2).                                                           | 1        | P34                   |

| TO0             | Output           | 16-bit timer (TM0) output (shared as 14-bit PWM output).                                                   | Input    | P30                   |

| TO1             | ]                | 8-bit timer (TM1) output.                                                                                  |          | P31                   |

| TO2             |                  | 8-bit timer (TM2) output.                                                                                  |          | P32                   |

| PCL             | Output           | Clock output (for main system clock, subsystem clock trimming).                                            | Input    | P35                   |

| BUZ             | Output           | Buzzer output.                                                                                             | Input    | P36                   |

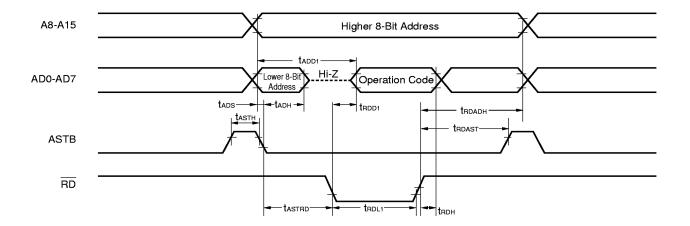

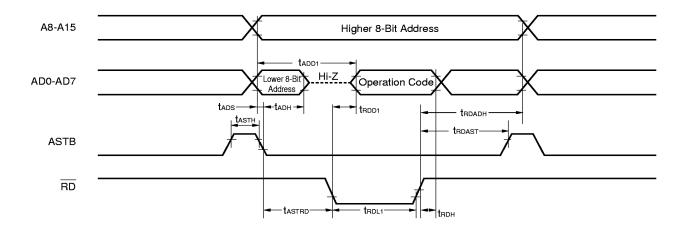

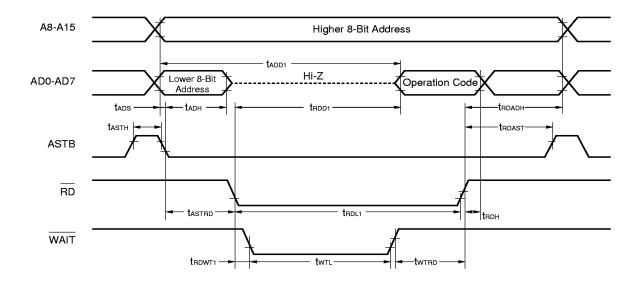

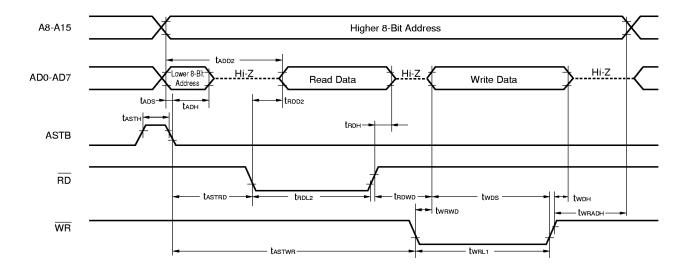

| AD0 to AD7      | Input<br>/output | Low-order address/data bus at external memory expansion.                                                   | Input    | P40 to P47            |

| A8 to A15       | Output           | High-order address bus at external memory expansion.                                                       | Input    | P50 to P57            |

| RD              | Output           | External memory read operation strobe signal output.                                                       | Input    | P64                   |

| WR              | ]                | External memory write operation strobe signal output.                                                      |          | P65                   |

| WAIT            | Input            | Wait insertion at external memory access.                                                                  | Input    | P66                   |

| ASTB            | Output           | Strobe output which latches the address information output at port 4 and port 5 to access external memory. | Input    | P67                   |

| ANI0 to ANI7    | Input            | A/D converter analog input.                                                                                | Input    | P10 to P17            |

| AVREF           | Input            | A/D converter reference voltage input.                                                                     | _        | _                     |

| AVDD            | _                | A/D converter analog power supply. Connected to V <sub>DD</sub> .                                          | _        | _                     |

| AVss            | <u> </u>         | A/D converter ground potential. Connected to Vss.                                                          | <u> </u> | _                     |

| RESET           | Input            | System reset input.                                                                                        | _        | _                     |

| X1              | Input            | Main system clock oscillation crystal connection.                                                          | -        | -                     |

| X2              |                  |                                                                                                            | _        | _                     |

| XT1             | Input            | Subsystem clock oscillation crystal connection.                                                            | Input    | P04                   |

| XT2             | _                |                                                                                                            | _        | _                     |

| V <sub>DD</sub> | _                | Positive power supply.                                                                                     | <u> </u> | _                     |

| Vss             | _                | Ground potential.                                                                                          | <u> </u> | _                     |

| IC              | -                | Internal connection. Connected to Vss directly.                                                            | -        | _                     |

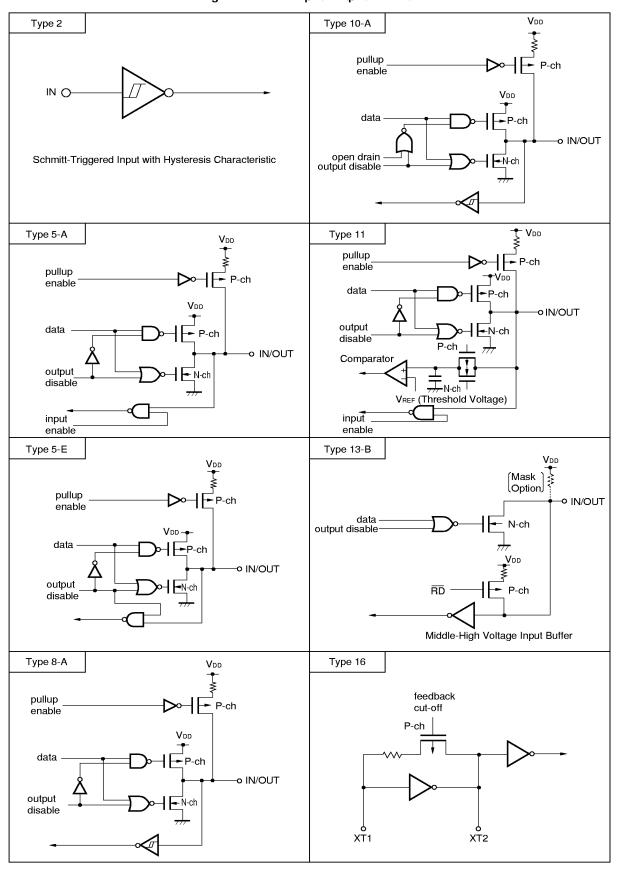

## 3.3 PIN I/O CIRCUITS AND RECOMMENDED CONNECTION OF UNUSED PINS

The input/output circuit type of each pin and recommended connection of unused pins are shown in Table 3-1. For the input/output circuit configuration of each type, see Figure 3-1.

Table 3-1. Input/Output Circuit Type of Each Pin

| Pin Name             | Input/output<br>Circuit Type | 1/0          | Recommended Connection when Not Used                                        |

|----------------------|------------------------------|--------------|-----------------------------------------------------------------------------|

| P00/INTP0/TI0        | 2                            | Input        | Connected to Vss.                                                           |

| P01/INTP1            | 8-A                          | Input/output | Individually connected to V <sub>SS</sub> via resistor.                     |

| P02/INTP2            |                              |              |                                                                             |

| P03/INTP3            |                              |              |                                                                             |

| P04/XT1              | 16                           | Input        | Connected to VDD or Vss.                                                    |

| P10/ANI0 to P17/ANI7 | 11                           | Input/output | Individually connected to V <sub>DD</sub> or V <sub>SS</sub> via resisitor. |

| P20/SI1              | 8-A                          |              |                                                                             |

| P21/SO1              | 5-A                          |              |                                                                             |

| P22/SCK1             | 8-A                          |              |                                                                             |

| P23/STB              | 5-A                          |              |                                                                             |

| P24/BUSY             | 8-A                          |              |                                                                             |

| P25/SI0/SB0          | 10-A                         |              |                                                                             |

| P26/SO0/SB1          |                              |              |                                                                             |

| P27/SCK0             |                              |              |                                                                             |

| P30/TO0              | 5-A                          |              |                                                                             |

| P31/TO1              |                              |              |                                                                             |

| P32/TO2              |                              |              |                                                                             |

| P33/TI1              | 8-A                          |              |                                                                             |

| P34/TI2              |                              |              |                                                                             |

| P35/PCL              | 5-A                          |              |                                                                             |

| P36/BUZ              |                              |              |                                                                             |

| P37                  |                              |              |                                                                             |

| P40/AD0 to P47/AD7   | 5-E                          |              | Individually connected to VDD via resistor.                                 |

| P50/A8 to P57/A15    | 5-A                          |              | Individually connected to V <sub>DD</sub> or V <sub>SS</sub> via resistor.  |

| P60 to P63           | 13-B                         |              | Individually connected to VDD via resistor.                                 |

| P64/RD               | 5-A                          |              | Individually connected to V <sub>DD</sub> or V <sub>SS</sub> via resistor.  |

| P65/WR               |                              |              |                                                                             |

| P66/WAIT             |                              |              |                                                                             |

| P67/ASTB             |                              |              |                                                                             |

| RESET                | 2                            | Input        | _                                                                           |

| XT2                  | 16                           | _            | Leave open.                                                                 |

| AVREF                |                              |              | Connected to Vss.                                                           |

| AVDD                 |                              |              | Connected to VDD.                                                           |

| AVss                 |                              |              | Connected to Vss.                                                           |

| IC                   |                              |              | Connected to Vss directly.                                                  |

Figure 3-1. Pin Input/Output Circuits

### 4. MEMORY SPACE

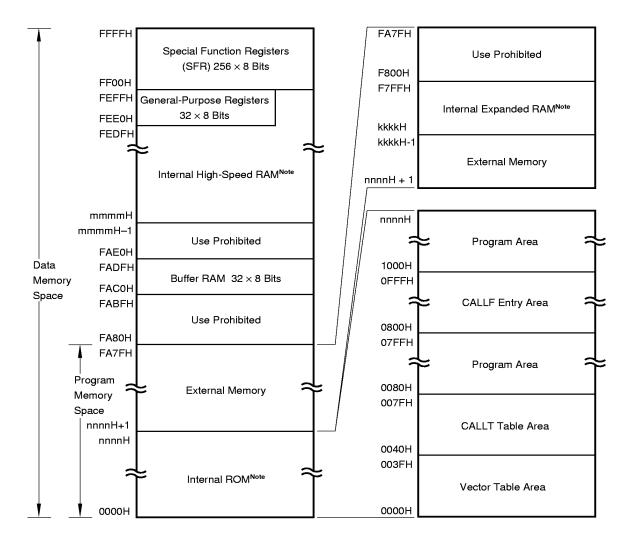

The memory map of the  $\mu$ PD78011F(A), 78012F(A), 78013F(A), 78014F(A), 78015F(A), 78016F(A), and 78018F(A) is shown in Figures 4-1 and 4-2.

**FFFFH** Special Function Registers (SFR) 256 × 8 Bits FF00H **FEFFH** General-Purpose Registers  $32 \times 8$  Bits **FEE0H** FEDFH Internal High-Speed RAMNote mmmmH nnnnH mmmmH-1 Use Prohibited Program Area FAE0H 1000H Data FADFH Buffer RAM 32 × 8 Bits Memory **OFFFH** FAC0H Space **CALLF Entry Area** FABFH Use Prohibited 0800H FA80H 07FFH FA7FH Program Area Program 0080H External Memory Memory 007FH Space nnnnH+1 **CALLT Table Area** nnnnH 0040H 003FH Internal ROMNote Vector Table Area 0000H 0000H

Figure 4-1. Memory Map (μPD78011F(A), 78012F(A), 78013F(A), 78014F(A))

Note Internal ROM and internal high-speed RAM capacities vary depending on the product (see the table below).

| Product Name | Intenal ROM End Address<br>nnnnH | Internal High-Speed RAM<br>Start Address<br>mmmmH |

|--------------|----------------------------------|---------------------------------------------------|

| μPD78011F(A) | 1FFFH                            | FD00H                                             |

| μPD78012F(A) | 3FFFH                            |                                                   |

| μPD78013F(A) | 5FFFH                            | FB00H                                             |

| μPD78014F(A) | 7FFFH                            |                                                   |

Figure 4-2. Memory Map (μPD78015F(A), 78016F(A), 78018F(A))

**Note** Internal ROM, internal high-speed RAM and internal extended RAM capacities vary depending on the product (see the table below).

| Product Name | Intenal ROM End Address<br>nnnnH | Internal High-Speed RAM<br>Start Address<br>mmmmH | Internal Extended RAM<br>Start Address<br>kkkkH |

|--------------|----------------------------------|---------------------------------------------------|-------------------------------------------------|

| μPD78015F(A) | 9FFFH                            | FB00H                                             | F600H                                           |

| μPD78016F(A) | BFFFH                            |                                                   |                                                 |

| μPD78018F(A) | EFFFH                            |                                                   | F400H                                           |

## 5. PERIPHERAL HARDWARE FUNCTION FEATURES

### 5.1 PORTS

The I/O port has the following three types

CMOS input (P00, P04)

CMOS input/output (P01 to P03, port 1 to port 5, P64 to P67)

N-ch open-drain input/output(15V withstand voltage) (P60 to P63)

Total

Table 5-1. Functions of Ports

| Port Name | Pin Name   | Function                                                                      |

|-----------|------------|-------------------------------------------------------------------------------|

| Port 0    | P00, P04   | Dedicated Input port                                                          |

|           | P01 to P03 | Input/output ports. Input/output can be specified bit-wise.                   |

|           |            | When used as an input port, on-chip pull-up resistor can be used by software. |

| Port 1    | P10 to P17 | Input/output ports. Input/output can be specified bit-wise.                   |

|           |            | When used as an input port, on-chip pull-up resistor can be used by software. |

| Port 2    | P20 to P27 | Input/output ports. Input/output can be specified bit-wise.                   |

|           |            | When used as an input port, on-chip pull-up resistor can be used by software. |

| Port 3    | P30 to P37 | Input/output ports. Input/output can be specified bit-wise.                   |

|           |            | When used as an input port, on-chip pull-up resistor can be used by software. |

| Port 4    | P40 to P47 | Input/output ports. Input/output can be specified in 8-bit units.             |

|           |            | When used as an input port, on-chip pull-up resistor can be used by software. |

|           |            | Test input flag (KRIF) is set to 1 by falling edge detection.                 |

| Port 5    | P50 to P57 | Input/output ports. Input/output can be specified bit-wise.                   |

|           |            | When used as an input port, on-chip pull-up resistor can be used by software. |

|           |            | LED can be driven directly.                                                   |

| Port 6    | P60 to P63 | N-ch open-drain input/output port. Input/output can be specified bit-wise.    |

|           |            | On-chip pull-up resistor can be specified by mask option.                     |

|           |            | LED can be driven directly.                                                   |

|           | P64 to P67 | Input/output ports. Input/output can be specified bit-wise.                   |

|           |            | When used as an input port, on-chip pull-up resistor can be used by software. |

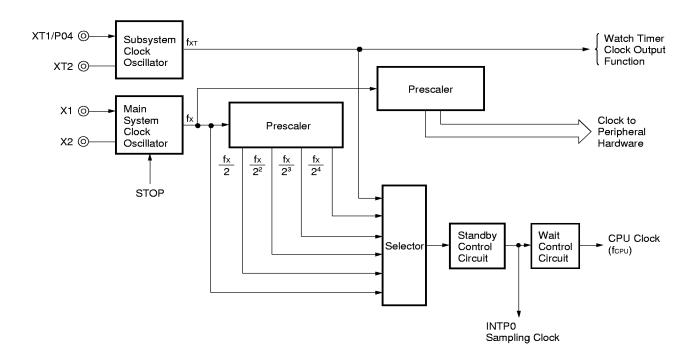

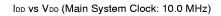

### **5.2 CLOCK GENERATOR**

There are two types of clock generator: main system clock and subsystem clock. The minimum instruction exection time can be changed.

- $0.4\mu$ s/ $0.8\mu$ s/ $1.6\mu$ s/ $3.2\mu$ s/ $6.4\mu$ s (Main system clock: at 10.0 MHz operation)

- 122μs (Subsystem clock: at 32.768 KHz operation)

Figure 5-1. Clock Generator Block Diagram

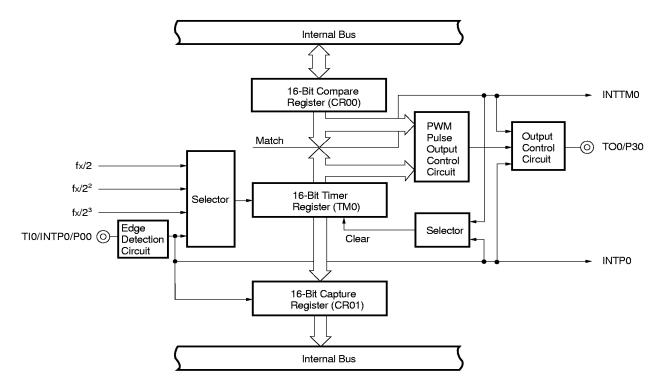

### **5.3 TIMER/EVENT COUNTER**

The following five channels are incorporated in the timer/event counter.

16-bit timer/event counter

8-bit timer/event counter

2 channels

Watch timer

1 channel

Watchdog timer

1 channel

Table 5-2. Types and Functions of Timer/Event Counter

|           |                          | 16-bit Timer/Event<br>Counter | 8-bit Timer/Event<br>Counter | Watch Timer | Watchdog Timer |

|-----------|--------------------------|-------------------------------|------------------------------|-------------|----------------|

| Туре      | Interval timer           | 1 channel                     | 2 channels                   | 1 channel   | 1 channel      |

|           | Externanal event counter | 1 channel                     | 2 channels                   | _           | _              |

| Functions | Timer output             | 1 output                      | 2 outputs                    | _           | _              |

|           | PWM output               | 1 output                      | _                            | _           | _              |

|           | Pulse width mesurement   | 1 input                       | -                            | _           | _              |

|           | Sqare wave output        | 1 output                      | 2 outputs                    | _           | _              |

|           | Interrupt request        | 2                             | 2                            | 1           | 1              |

|           | Test input               | _                             | -                            | 1 input     | _              |

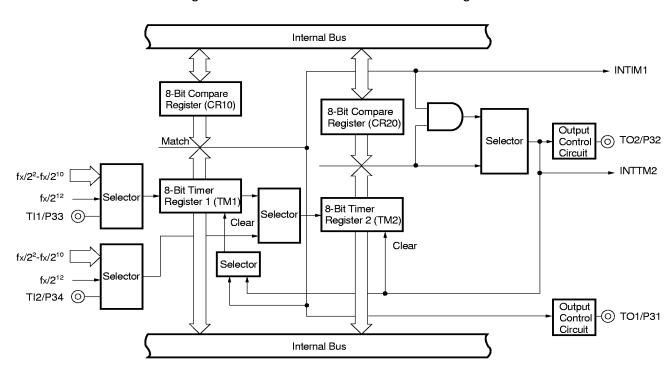

Figure 5-2. 16-bit Timer/Enent Counter Block Diagram

Figure 5-3. 8-bit Timer/Enent Counter Block Diagram

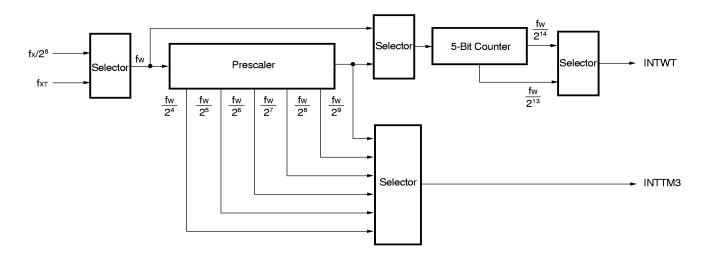

Figure 5-4. Watch Timer Block Diagram

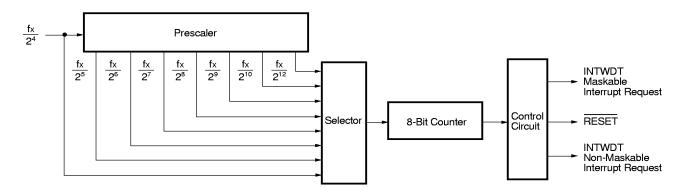

Figure 5-5. Watchdog Timer Block Diagram

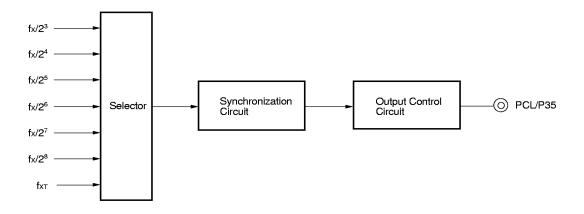

#### 5.4 CLOCK OUTPUT CONTROL CIRCUIT

The clock with the following frequencies can be output for clock output.

- 39.1 kHz/78.1 kHz/156 kHz/313 kHz/625 kHz/1.25 MHz (Main system clock: at 10.0 MHz operation)

- 32.768 kHz (Subsystem clock: at 32.768 kHz operation)

Figure 5-6. Clock Output Control Block Diagram

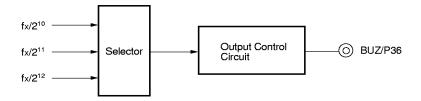

### 5.5 BUZZER OUTPUT CONTROL CIRCUIT

The clock with the following frequencies can be output for buzzer output.

• 2.4 kHz/4.9 kHz/9.8 kHz (Main system clock: at 10.0 MHz operation)

Figure 5-7. Buzzer Output Control Block Diagram

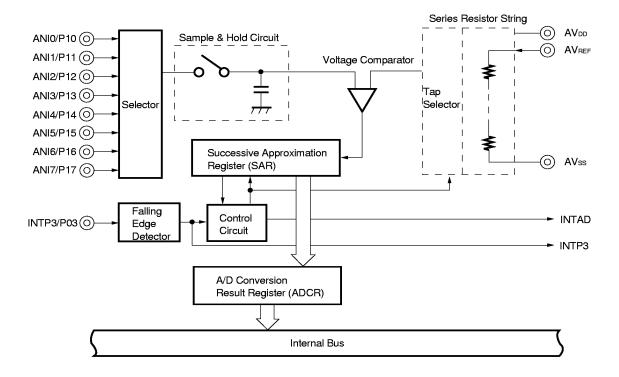

## 5.6 A/D CONVERTER

The A/D converter has on-chip eight 8-bit resolution channels. There are the following two method to start A/D conversion.

- · Hardware starting

- · Software starting

Figure 5-8. A/D Converter Block Diagram

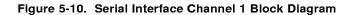

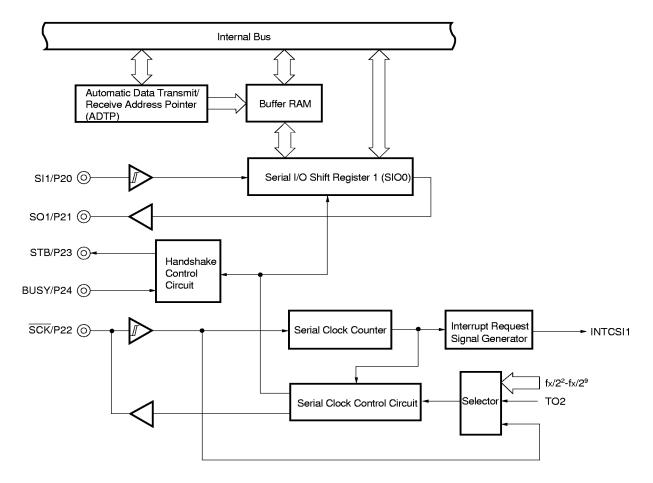

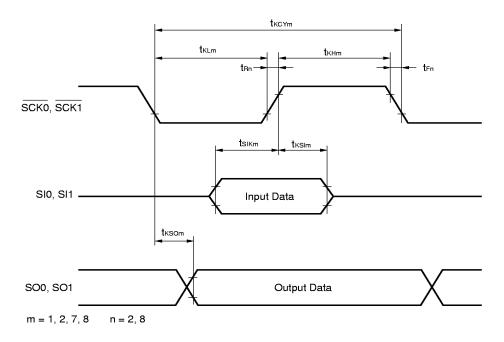

## 5.7 SERIAL INTERFACES

There are two on-chip clocked serial interfaces as follows.

- Serial Interface channel 0

- · Serial Interface channel 1

Table 5-3. Type and Function of Serial Interface

| Function                                   | Serial Interface Channel 0   | Serial Interface Channel 1   |

|--------------------------------------------|------------------------------|------------------------------|

| 3-wire serial I/O mode                     | O (MSB/LSB-first switchable) | O (MSB/LSB-first switchable) |

| 3-wire serial I/O mode with automatic data | -                            | O (MSB/LSB-first switchable) |

| transmit/receive function                  |                              |                              |

| SBI (Serial Bus Interface) mode            | O (MSB-first)                | -                            |

| 2-wire serial I/O mode                     | O (MSB-first)                | -                            |

Internal Bus SI0/SB0/P25 (0) Serial I/O Shift Output Selector Register 0 (SIO0) Latch SO0/SB1/P26 (O) Busy/Acknowledge Output Circuit Bus Release/Command/ Selector Acknowledge Detection Circuit Interrupt Request ► INTCSI0 SCKO/P27 (O) Signal Serial Clock Counter Generator  $fx/2^2-fx/2^9$ Serial Clock TO2 Selector Control Circuit

Figure 5-9. Serial Interface Channel 0 Block Diagram

## 6. INTERRUPT FUNCTIONS AND TEST FUNCTIONS

### **6.1 INTERRUPT FUNCTIONS**

There are the 14 interrupt sources of 3 different kind as shown below.

Non-maskable: 1Maskable: 12Software: 1

Table 6-1. Interrupt Source List

|                | Default         |         | Interrupt Source                                              | Internal/ | Vector Table | Basic                        |

|----------------|-----------------|---------|---------------------------------------------------------------|-----------|--------------|------------------------------|

| Interrupt Type | Priority Note 1 | Name    | Trigger                                                       | External  | Address      | Configuration<br>Type Note 2 |

| Non-maskable   | _               | INTWDT  | Watchdog timer overflow (with watchdog timer mode 1 selected) | Internal  | 0004H        | (A)                          |

| Maskable       | 0               | INTWDT  | Watchdog timer overflow (with interval timer mode selected)   |           |              | (B)                          |

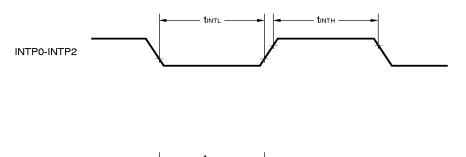

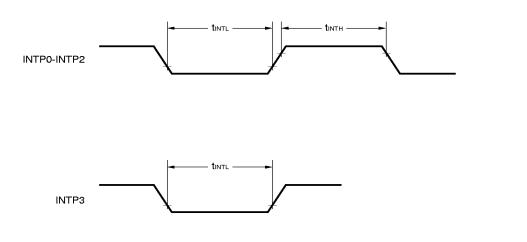

|                | 1               | INTP0   | Pin input edge detection                                      | External  | 0006H        | (C)                          |

| 2              |                 | INTP1   |                                                               |           | 0008Н        | (D)                          |

| 3              | INTP2           |         |                                                               | 000AH     |              |                              |

|                | 4               | INTP3   |                                                               |           | 000CH        |                              |

|                | 5               | INTCSI0 | Serial interface channel 0 transfer end                       | Internal  | 000EH        | (B)                          |

|                | 6               | INTCSI1 | Serial interface channel 1 transfer end                       |           | 0010H        |                              |

|                | 7               | INTTM3  | Reference time interval signal from watch timer               |           | 0012H        |                              |

|                | 8               | INTTM0  | 16 bit timer/event counter match signal generation            |           | 0014H        |                              |

|                | 9               | INTTM1  | 8-bit timer/event counter 1 match signal generation           |           | 0016H        |                              |

|                | 10              | INTTM2  | 8-bit timer/event counter 2 match signal generation           |           | 0018H        |                              |

|                | 11              | INTAD   | A/D converter conversion end                                  |           | 001AH        |                              |

| Software       |                 | BRK     | BRK instruction execution                                     |           | 003EH        | (E)                          |

**Notes 1.** The default pririty is the priority applicable when more than one maskable interrupt request is generated. 0 is the highest priority and 11, the lowest.

2. Basic configuration types (A) to (E) correspond to (A) to (E) on the next page.

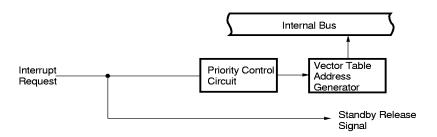

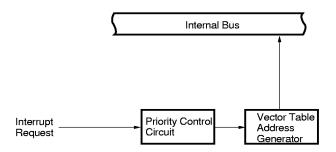

Figure 6-1. Basic Interrupt Function Configuration (1/2)

## (A) Internal Non-Maskable Interrupt

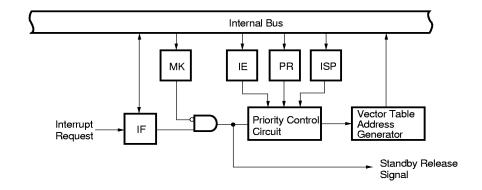

### (B) Internal Maskable Interrupt

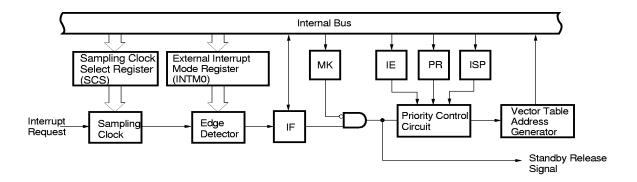

## (C) External Maskable Interrupt (INTP0)

Figure 6-1. Basic Interrupt Function Configuration (2/2)

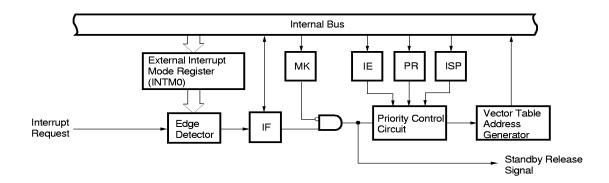

## (D) External Maskable Interrupt (Except INTP0)

## (E) Software Interrupt

IF : Interrupt request flag

IE : Interrupt enable flag

ISP : In-service priority flag

MK : Interrupt mask flag

PR : Priority specification flag

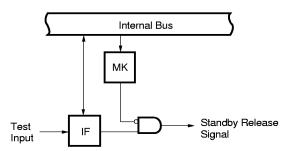

## **6.2 TEST FUNCTIONS**

There are two test sources as shown in Table 6-2.

Table 6-2. Test Source List

|        | Test Source                   | Internal/External |

|--------|-------------------------------|-------------------|

| Name   | Trigger                       | mterna/External   |

| INTWT  | Watch timer overflow          | Internal          |

| INTPT4 | Port 4 falling edge detection | External          |

Figure 6-2. Test Function Basic Configuration

IF : Test input flagMK : Test mask flag

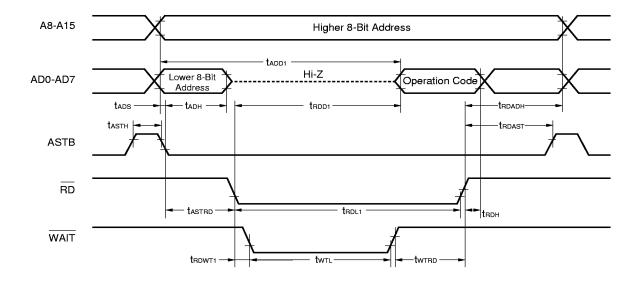

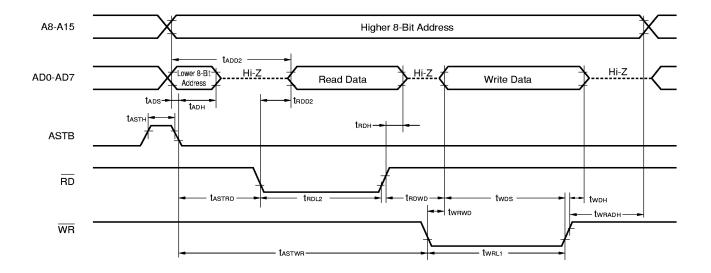

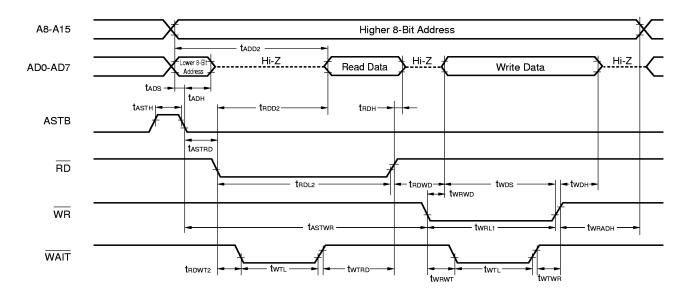

#### 7. EXTERNAL DEVICE EXPANSION FUNCTIONS

The external device expansion function is used to connect external devices to areas other than the internal ROM, RAM and SFR.

Ports 4 to 6 are used for connection with external devices.

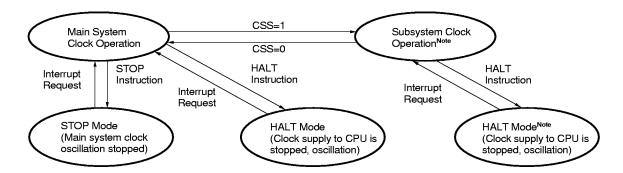

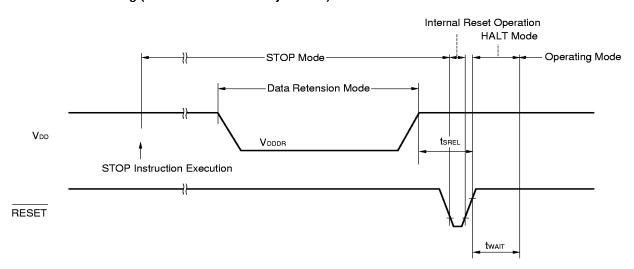

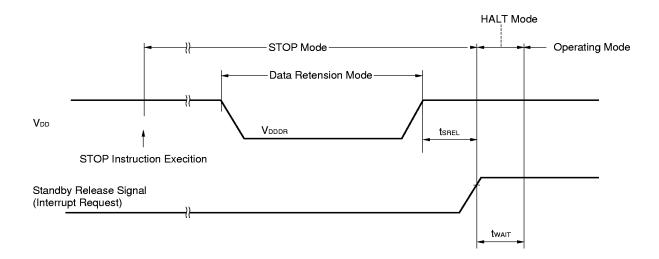

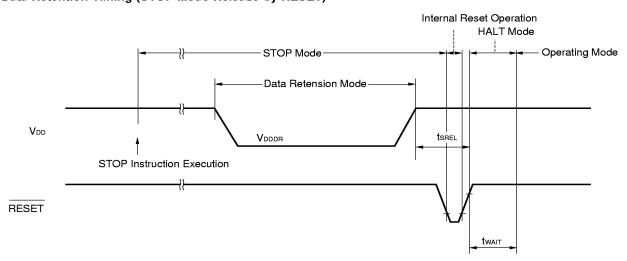

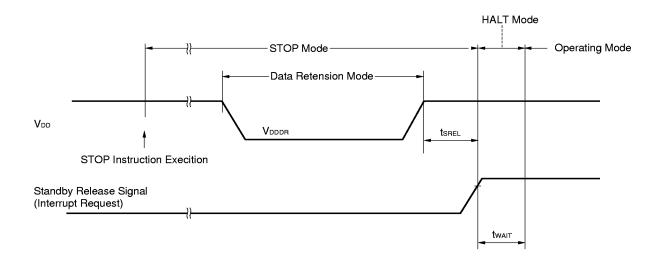

#### 8. STANDBY FUNCTIONS

There are the following two standby functions to reduce the current consumption.

• HALT mode : The CPU operating clock is stopped. The average consumption current can be reduced by intermittent operation in combination with the normal operat ing mode.

• STOP mode : The main system clock oscillation is stopped. The whole operation by the main system clock is stopped, so that the system operates with ultra-low power consumption using only the subsystem clock.

Figure 8-1. Standby Functions

**Note** The current consumption can be reduced by stopping the main system clock. When the CPU is operating on the subsystem clock, set bit 7 (MCC) of the processor clock control register (PCC) to stop the main system clock. The STOP instruction cannot be used.

Caution When the main system clock is stopped and the system is operated by the subsystem clock, the subsystem clock should be switched again to the main system clock after the oscillation stabilization time is secured by the program by the program.

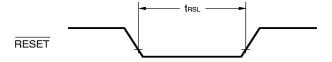

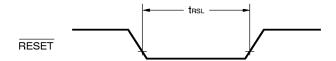

## 9. RESET FUNCTIONS

There are the following two reset methods.

- External reset input by RESET pin.

- Internal reset by watchdog timer hung-up time detection.

## 10. INSTRUCTION SET

## (1) 8-Bit Instruction

MOV, XCH, ADD, ADDC, SUB, SUBC, AND, OR, XOR, CMP, MULU, DIVUW, INC, DEC, ROR, ROL, RORC, ROLC, ROR4, ROL4, PUSH, POP, DBNZ

| Note   Sfr   Saddr   Iaddr16   PSW   [DE]   [HL]   [HL+B]   Saddr16   Interpretation   In |              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| ADDC   SUB   ADD   ADD | None         |

| B, C DBNZ  saddr MOV MOV  ADD ADDC SUB SUBC AND OR XOR CMP  DBNZ  DBNZ  DBNZ  DBNZ  DBNZ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | c            |

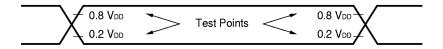

| sfr MOV MOV saddr MOV MOV ADD ADDC SUB SUBC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | INC<br>DEC   |